## Lecture Notes in Computer Science

3756

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Jiannong Cao Wolfgang Nejdl Ming Xu (Eds.)

# Advanced Parallel Processing Technologies

6th International Workshop, APPT 2005 Hong Kong, China, October 27-28, 2005 Proceedings

#### Volume Editors

Jiannong Cao Hong Kong Polytechnic University Hung Hom, Kowloon, Hong Kong, China E-mail: csjcao@comp.polyu.edu.hk

Wolfgang Nejdl University of Hannover, Information Systems Institute Knowledge Based Systems (KBS), L3S Research Center Appelstr. 4, 30167 Hannover, Germany E-mail: nejdl@13s.de

Ming Xu National University of Defense Technology Department of Networking Engineering, Computer College Changsha, Hunan 410073, China E-mail: xuming64@public.cs.hn.cn

Library of Congress Control Number: 2005934413

CR Subject Classification (1998): D, B, C, F.1-3, G.1-2

ISSN 0302-9743

ISBN-10 3-540-29639-5 Springer Berlin Heidelberg New York ISBN-13 978-3-540-29639-3 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11573937 06/3142 5 4 3 2 1 0

## **Preface**

Welcome to the proceedings of APPT 2005: the 6th International Workshop on Advanced Parallel Processing Technologies. APPT is a biennial workshop on parallel and distributed processing. Its scope covers all aspects of parallel and distributed computing technologies, including architectures, software systems and tools, algorithms, and applications. APPT originated from collaborations by researchers from China and Germany and has evolved to be an international workshop. APPT 2005 was the sixth in the series. The past five workshops were held in Beijing, Koblenz, Changsha, Ilmenau, and Xiamen, respectively.

The Program Committee is pleased to present the proceedings for APPT 2005. This year, APPT 2005 received over 220 submissions from researchers all over the world. All the papers were peer reviewed by two to three Program Committee members on their relevance, originality, significance, technical quality, and presentation. Based on the review result, 55 high-quality papers were selected to be included in the proceedings. The papers in this volume represent the forefront of research on parallel processing and related fields by researchers from China, Germany, USA, Korea, India, and other countries. The papers accepted cover a wide range of exciting topics, including architectures, software, networking, and applications.

The excellent program was the result of the hard work and the collective effort of many people and organizations. We would like to express our special thanks to the Architecture Professional Committee of the China Computer Federation (APC-CCF), the Hong Kong Polytechnic University, the National University of Defense Technology, China, and the Harbin Institute of Technology, China. We would like to thank the general chair, Prof. Xingming Zhou, and the general co-chairs, Prof. Xiaodong Zhang and Prof. David Bader, for their great support. Thanks to all members of the Program Committee and all the other reviewers for the time and hard work they put into the thorough reviewing of the large number of papers. We appreciate the keynote speakers, Prof. Francis C.M. Lau and Prof. Kurt Rothermel, for their strong support of the program. We would also like to express our gratitude to Springer for its assistance in putting the proceedings together. Last but not least, our thanks go to the Local Organizing Committee for the great job it did in making the local arrangements and organizing an attractive social program. Without their dedicated help and diligent work, the workshop would not have been so successful.

We would like to take this opportunity to thank all the authors, many of whom traveled great distances to participate in this workshop and make their

## VI Preface

valuable contributions. We hope that all participants enjoyed the program and found it worthwhile. We warmly welcome any comments and suggestions to improve our work.

August 2005

Jiannong Cao Wolfgang Nejdl Ming Xu

## Organization

APPT 2005 was organized mainly by the Department of Computing, Hong Kong Polytechnic University and the National University of Defense Technology, China.

## **Executive Committee**

General Chair Xingming Zhou

(Member of Chinese Academy of Sciences, National Lab for Parallel and Distributed

Processing, China)

General Vice Co-chairs Xiaodong Zhang

(College of William and Mary, USA)

David A. Bader

(Georgia Institute of Technology, USA)

Program Co-chairs Jiannong Cao

(Hong Kong Polytechnic University, China)

Wolfgang Nejdl

(University of Hannover, Germany)

Publicity Chair Cho-Li Wang

(University of Hong Kong, China)

Publication Chair Laurence T. Yang

(St. Francis Xavier University, Canada)

Local Organization Chair Allan K.Y. Wong

(Hong Kong Polytechnic University, China)

Finance/Registration Chair Ming Xu

(National Lab for Parallel and Distributed

Processing, China)

## **Sponsoring Institutions**

Architecture Professional Committee of the China Computer Federation, China

Hong Kong Polytechnic University, China

National University of Defense Technology, China

Association for Computing Machinery, Hong Kong Chapter

Springer

## **Program Committee**

Srinivas Aluru Jose Nelson Amaral

Wentong Cai Yiu-Keung Chan Tarek El-Ghazawi

Binxing Fang John Feo Guang Gao

Ananth Grama

Manfred Hauswirth Bruce Hendrickson Mehdi Jazayeri Zhenzhou Ji Ashfaq Khokhar Ajay Kshemkalyani

Francis Lau Xiaoming Li Xinsong Liu

Yunhao Liu

Xinda Lu Siwei Luo Beth Plale

Bernhard Plattner

Sartaj Sahni Nahid Shahmehri Chengzheng Sun Zhimin Tang Bernard Traversat Peter Triantafillou Xingwei Wang

Jie Wu Li Xiao

Lars Wolf

Chengzhong Xu Weimin Zheng Iowa State University, USA University of Alberta, Canada

Nanyang Technological University, Singapore

City University of Hong Kong, China

George Mason University, USA

Harbin Institute of Technology, China

Cray Inc., USA

University of Delaware, USA Purdue University, USA EPFL, Switzerland

Sandia National Laboratory, USA Technical University of Vienna, Austria Harbin Institute of Technology, China University of Illinois, Chicago, USA University of Illinois, Chicago, USA University of Hong Kong, China

Peking University, China

University of Electronic Sciences and Technology of China, China

Hong Kong University of Science and

Technology, China

Shanghai Jiao Tong University, China Northern Jiao Tong University, China

Indiana University, USA

${\bf Swiss} \ {\bf Federal} \ {\bf Institute} \ {\bf of} \ {\bf Technology},$

Switzerland

University of Florida, USA Linköping University, Sweden Griffith University, Australia

Institute of Computing, CAS, China

Sun Microsystems, USA University of Patras, Greece Northeastern University, China Technical University Braunschweig,

Germany

Florida Atlantic University, USA Michigan State University, USA Wayne State University, USA Tsinghua University, China

## **Table of Contents**

## Keynote Speech

| Research Issues in Adapting Computing to Small Devices  Francis C.M. Lau                                                                    | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Mobile Context-Aware Systems – Linking the Physical and Digital World  **Kurt Rothermel                                                     | 2  |

| Architecture                                                                                                                                |    |

| A Data Transformations Based Approach for Optimizing Memory and Cache Locality on Distributed Memory Multiprocessors  Xia Jun, Xue-Jun Yang | 3  |

| A Fetch Policy Maximizing Throughput and Fairness for Two-Context SMT Processors                                                            | 10 |

| Caixia Sun, Hongwei Tang, Minxuan Zhang                                                                                                     | 13 |

| A Loop Transformation Using Two Parallel Region Partitioning Method Sam Jin Jeong, Jung Soo Han                                             | 23 |

| Criticality Based Speculation Control for Speculative Multithreaded Architectures  Rahul Nagpal, Anasua Bhowmik                             | 31 |

| Design and Implementation of Semantic Caching Coherency Control<br>Scheme Toward Distributed Environment<br>Hai Wan, Lei Li                 | 41 |

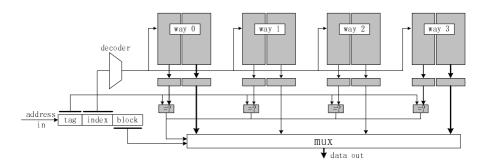

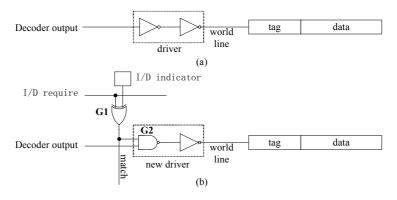

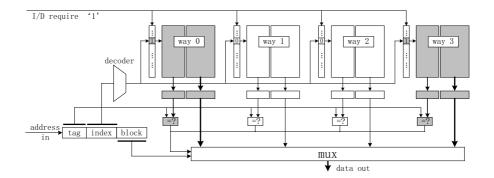

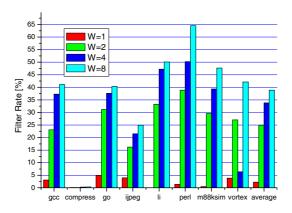

| Energy Efficient United L2 Cache Design with Instruction/Data Filter Scheme  Zhiqiang Ma, Zhenzhou Ji, Mingzeng Hu, Yi Ji                   | 52 |

| Improving Latency Tolerance of Network Processors Through<br>Simultaneous Multithreading                                                    |    |

| Bo Liang, Hong An, Fang Lu, Rui Guo                                                                                                         | 61 |

Χ

| Vector Space Based on Hierarchical Weighting: A Component Ranking<br>Approach to Component Retrieval                                       |     |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Gui Gui, Paul D. Scott                                                                                                                     | 184 |

| System and Software                                                                                                                        |     |

| A High Availability Mechanism for Parallel File System  Hu Zhang, Weiguo Wu, Xiaoshe Dong, Depei Qian                                      | 194 |

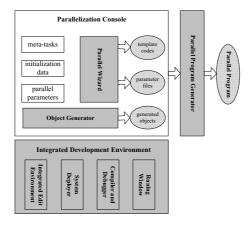

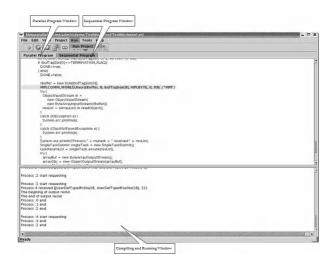

| A User-Guided Semi-automatic Parallelization Method and Its<br>Implementation  Chuliang Weng, Zhongguo Chen, Xinda Lu, Minglu Li, Yong Yin | 204 |

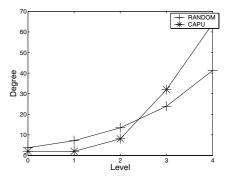

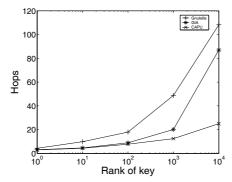

| CAPU: Enhancing P2P File Sharing System with Capacity Aware Topology                                                                       |     |

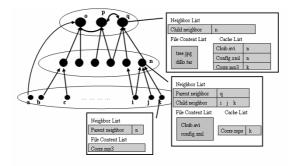

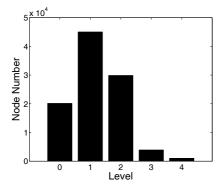

| Hongliang Yu, Weimin Zheng, Dongsheng Wang, Haitao Dong, Lu Li                                                                             | 214 |

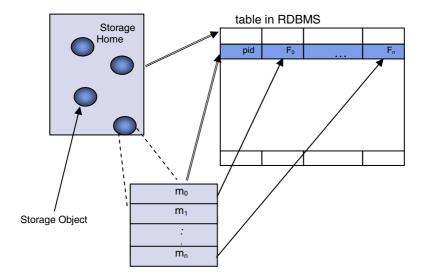

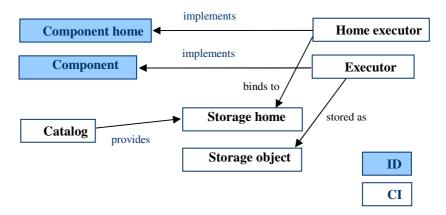

| Implementing Component Persistence in CCM Based on StarPSS  Jingbin An, Yan Jia, Zhiying Wang                                              | 226 |

| Load Balancing Design Issues on Prefetch-Based DSM Systems  Hsiao-Hsi Wang, Kuan-Ching Li, Kuo-Jen Wang, Ssu-Hsuan Lu,  Chun-Chieh Yang    | 234 |

| Task Assignment for Network Processor Pipelines Using GA  Shoumeng Yan, Xingshe Zhou, Lingmin Wang, Fan Zhang,  Haipeng Wang               | 244 |

| Test-Suite Reduction Using Genetic Algorithm  Xue-ying Ma, Bin-kui Sheng, Cheng-qing Ye                                                    | 253 |

| Grid Computing                                                                                                                             |     |

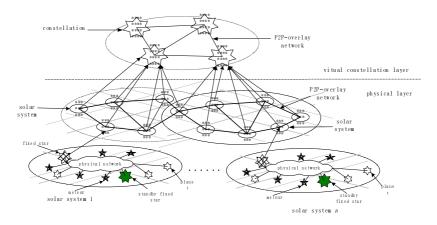

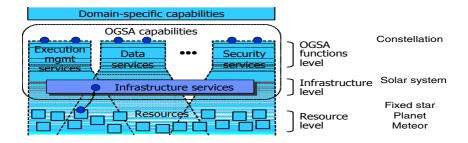

| A Constellation Model for Grid Resource Management  Yinfeng Wang, Xiaoshe Dong, Xiuqiang He, Hua Guo, Fang Zheng, Zhongsheng Qin           | 263 |

| An Effective Information Service Architecture in Grid Environment  Huashan Yu, Yin Luo, Xingguo Zhu, Xiaoming Li                           | 273 |

| An Efficient Data Management System with High Scalability for<br>ChinaGrid Support Platform                                                                          |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Hai Jin, Wenjun Gong, Song Wu, Muzhou Xiong, Li Qi, Chengwei Wang                                                                                                    | 282 |

| CGSP: An Extensible and Reconfigurable Grid Framework  Yongwei Wu, Song Wu, Huashan Yu, Chunming Hu                                                                  | 292 |

| Early Experience of Remote and Hot Service Deployment with Trustworthiness in CROWN Grid  Hailong Sun, Yanmin Zhu, Chunming Hu, Jinpeng Huai, Yunhao Liu, Jianxin Li | 301 |

| Grid Developing Environment in CGSP System  Weimin Zheng, Lisen Mu, Qing Wang, Yongwei Wu                                                                            | 313 |

| Grid Job Support System in CGSP  Jinpeng Huai, Yu Wan, Yong Wang, Haifeng Ou                                                                                         | 323 |

| JFreeSim: A Grid Simulation Tool Based on MTMSMR Model  Hai Jin, Jin Huang, Xia Xie, Qin Zhang                                                                       | 332 |

| OOML-Based Ontologies and Its Services for Information Retrieval in UDMGrid  Xixi Luo, Xiaowu Chen                                                                   | 342 |

| Networking                                                                                                                                                           |     |

| A Hybrid Integrated QoS Multicast Routing Algorithm in IP/DWDM Optical Internet  Xingwei Wang, Jia Li, Min Huang                                                     | 353 |

| An Efficient Distributed Broadcasting Algorithm for Ad Hoc Networks  Qiang Sun, Layuan Li                                                                            | 363 |

| Chaos-Based Dynamic QoS Scheme and Simulating Analysis  Qigang Zhao, Qunzhan Li                                                                                      | 373 |

| Dynamic Delaunay Triangulation for Wireless Ad Hoc Network  Ming Li, XiCheng Lu, Wei Peng                                                                            | 382 |

| Energy Efficient Multipath Routing in Large Scale Sensor Networks with Multiple Sink Nodes  Yuequan Chen, Edward Chan, Song Han                                      | 390 |

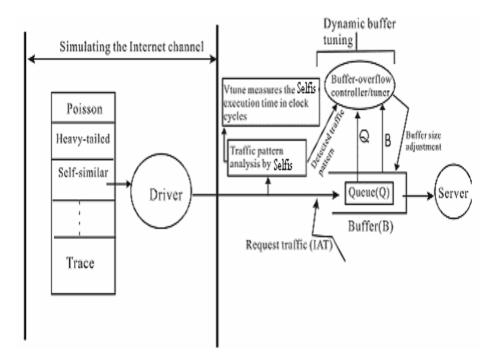

| FLC: A Novel Dynamic Buffer Tuner for Shortening Service Roundtrip<br>Time over the Internet by Eliminating User-Level Buffer Overflow on<br>the Fly |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Wilfred W.K. Lin, Allan K.Y. Wong, Tharam S. Dillon                                                                                                  | 400 |

| Intelligent Congestion Avoidance in Differentiated Service Networks  Farzad Habibipour, Ahmad Faraahi, Mehdi Glily                                   | 409 |

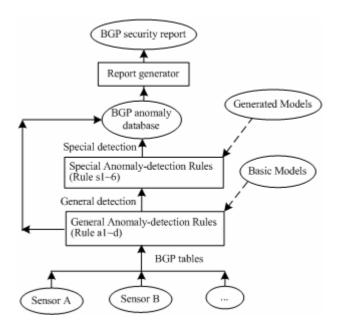

| Rule-Based Anomaly Detection of Inter-domain Routing System  Peidong Zhu, Xin Liu, Mingjun Yang, Ming Xu                                             | 417 |

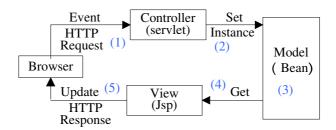

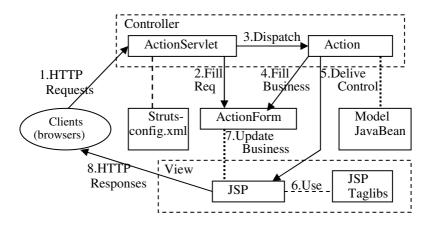

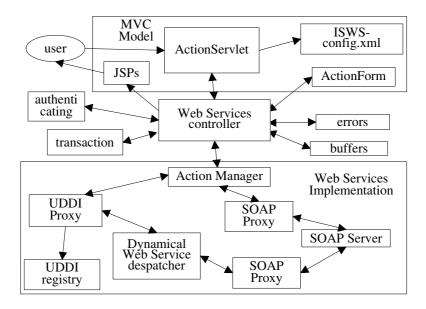

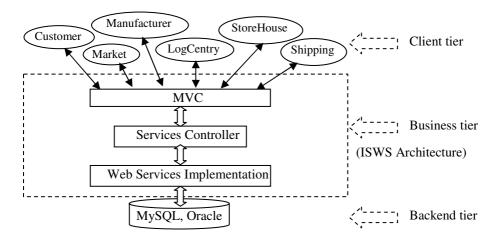

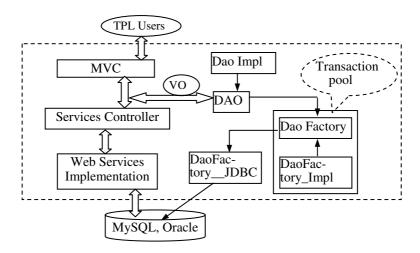

| Transaction of Web Services Based on Struts  Gong-Xuan Zhang, Ping-Li Wang, Wen Chen                                                                 | 427 |

| Applied Technologies                                                                                                                                 |     |

| A Method of Aggregate Query Matching in Semantic Cache for Massive Database Applications  Jianyu Cai, Yan Jia, Shuqiang Yang, Peng Zou               | 435 |

| A Parallel Modular Exponentiation Scheme for Transformed Exponents  Chin-Chen Chang, Yeu-Pong Lai                                                    | 443 |

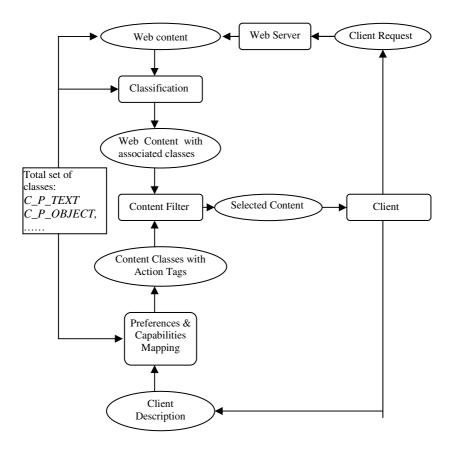

| Content Selection Model for Adaptive Content Delivery  Chen Ding, Shutao Zhang, Chi-Hung Chi                                                         | 453 |

| Dynamic Service Provisioning for Multiplayer Online Games  Jens Müller, Rafael Schwerdt, Sergei Gorlatch                                             | 461 |

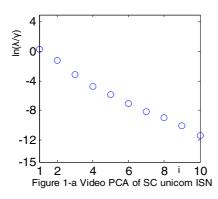

| Principal Component Analysis for Distributed Data Sets with Updating Zheng-Jian Bai, Raymond H. Chan, Franklin T. Luk                                | 471 |

| Priority Conscious Transaction Routing in a Real-Time Shared Disks Cluster  Kyungoh Ohn, Sangho Lee, Haengrae Cho                                    | 484 |

| Probabilistic Continuous Update Scheme in Location Dependent Continuous Queries  Song Han, Edward Chan                                               | 494 |

| SIP-Based Adaptive Multimedia Transmissions for Wired and Wireless Networks  Weijia Jia, Man-Ching Yuen                                              | 505 |

| The Copies to the State Clottery 1 were                                                                                                              | 500 |

## XIV Table of Contents

| WM+: An Optimal Multi-pattern String Matching Algorithm Based on the WM Algorithm |     |

|-----------------------------------------------------------------------------------|-----|

| Xunxun Chen, Binxing Fang, Lei Li, Yu Jiang                                       | 515 |

|                                                                                   |     |

| Author Index                                                                      | 525 |

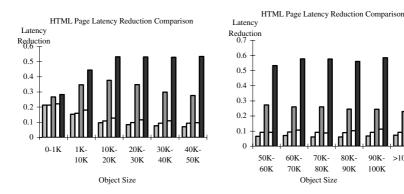

## Research Issues in Adapting Computing to Small Devices

Francis C.M. Lau

Department of Computer Science, The University of Hong Kong, China fcmlau@cs.hku.hk

Abstract. Advances in pervasive and mobile technologies are making computing available to us at anytime anywhere. Availability however does not automatically mean it is in a form that implies ease of use. Usability in the mobile world amounts to a set of problems that are not so much precedented in the history of computing. Handheld mobile devices that are thin-lean-mean for instance present challenges that require fundamental changes in the way computation is carried out, its architecture, or its supporting environment. A practical goal is to minimize these changes, which calls for automatic or semi-automatic adaptation of existent computing to the small devices. We discuss the issues and research challenges of "X adapting to Y", where X includes content, data, code, computation, GUI, and so on, and the changes in semantics and/or syntax due to the adaptation are to satisfy the constraints of Y. Some experiments we have carried out for content and code adaptation provide some useful illustration.

## Mobile Context-Aware Systems – Linking the Physical and Digital World

#### Kurt Rothermel

Institute of Parallel and Distributed Systems and Centre of Excellence Nexus,

Universität Stuttgart, Germany

Kurt.Rothermel@informatik.uni-stuttgart.de

Abstract. The rapid miniaturisation and decline in prices of computer, communication and sensor technology give rise to a number of interesting developments, such as multifunctional mobile devices, sensor platforms embedded into everyday things, and sensor nodes organised in a wireless network. Those systems can capture and process sensory data and communicate this information to other peers in their proximity or to an existing server infrastructure. The sensory data are fed into spatio-temporal models of the physical world, which build the basis for the promising class of context-aware applications. Based on these developments it can be anticipated that there will be billions of sensor systems in our physical environment near future. Consequently, we envision most of the future applications to be context-aware, sharing highly dynamic digital world models offered by a large number of content providers. Obviously, the realisation of this vision will cause a number of both technological and social challenges. Some of these challenges are subject to the research of Nexus, a Centre of Excellence established at University of Stuttgart in the year 2003. In this talk, we present the vision and objectives of Nexus. Moreover, we will discuss some aspects of scaleable context management.

## A Data Transformations Based Approach for Optimizing Memory and Cache Locality on Distributed Memory Multiprocessors\*

Xia Jun and Xue-Jun Yang

School of Computer Science, National University of Defense Technology, Changsha 410073, Hunan, China

**Abstract.** Data locality is one of the key factors in affecting the performance of parallel programs running on distributed memory multiprocessors. This paper presents an approach for optimizing memory locality and cache locality of perfect or non-perfect loop nests using linear data transformations on distributed memory multiprocessors. The approach optimizes memory locality with the data space fusion technique and cache locality with the projection-delamination technique, and combines the both techniques effectively to make the overheads of remote memory accesses and local memory accesses as low as possible. We conduct experiments with nine programs and the results show the approach is effective in optimizing memory locality and cache locality simultaneously.

#### 1 Introduction

Data locality has an important affection on the performance of parallel programs running on distributed memory multiprocessors. Generally, the locality optimization problem on distributed memory multiprocessors can be divided into two subproblems. One is the memory locality optimization problem. For distributed memory multiprocessors, the memory access time from a processor to its own local memory is generally much faster than the time to local memory of the other processors. Hence, an efficient parallel executing program requires programmers or compilers to distribute code and data carefully to reduce remote memory access overheads. The other is the cache locality optimization problem. When a processor accesses its local memory, good cache locality can improve cache hit rate and reduce local memory access overheads.

Over the last decade, a great number of researchers have paid attention to the memory locality optimization problem for distributed memory multiprocessors [1-3]. Chen and Chang [1] present a skewed alignment instead of traditional dimension-order alignment techniques to align arrays. Chang et al. [2] present two new alignment functions for loop iteration space and arrays with linear subscripts in three loop index variables or quadratic subscripts. Xia and Yang [3] give an approach of effec-

<sup>\*</sup> This research is supported by NNSF (National Natural Science Foundation grant No. 69825104).

J. Cao, W. Nejdl, and M. Xu (Eds.): APPT 2005, LNCS 3756, pp. 3 – 12, 2005. © Springer-Verlag Berlin Heidelberg 2005

tive alignment of computation and data for a sequence of perfect loop nests. All the above researchers only consider memory locality optimization and their approaches are effective to reduce remote memory access overheads on distributed memory multiprocessors. As they don't consider cache locality optimization, there may exist many local memory access overheads because of bad cache locality, which may prevent the whole performance of parallel programs from improving further.

Over the last decade, many researchers also used loop transformations [4-6], data transformations [7-9] and combined loop and data transformations [10-12] to optimize cache locality. We discuss the most related of their work in the following.

**Loop Transformations.** Wolf and Lam [4] show how to use unimodular loop transformations followed by tiling loops that carry some form of reuse to improve locality. McKinley et al. [5] present a method that considers loop fusion, distribution, permutation, and reversal for improving locality. Bik et al. [6] present a method that can simultaneously reshape the access patterns of several occurrences of multi-dimensional arrays along certain desired access directions.

**Data Transformations.** Clauss et al. [7] use the parameterized polyhedra theory and Ehrhart polynomials to provide a new array reference evaluation function to the compiler, such that the data layout corresponds exactly to the utilization order of these data. Kandemir et al. [8] present a hyperplane based approach for optimizing spatial locality in loop nests. Xia et al. [9] present a projection-delamination technique for optimizing spatial locality and a data transformation framework based on it.

Combined Loop and Data Transformations. Cierniak and Li [10] use loop and array dimension permutations in an exhaustive search to determine the appropriate loop and data transformations. Kandemir et al. [11] give a matrix-based approach for optimizing the global locality using loop and data transformations. Kandemir et al. [12] use integer linear programming and the memory layout graph to find the best combination of loop and data layout transformations for optimizing the global locality.

The above researchers only consider cache locality optimization and their approaches are effective to improve cache hit rate and reduce local memory access overheads. As they don't consider memory locality optimization, their approaches are more suitable for use in uniprocessors or shared memory multiprocessors than in distributed memory multiprocessors because of remote memory access overheads.

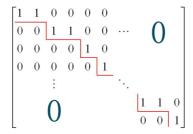

In this paper, we present an approach for simultaneously optimizing memory locality and cache locality through linear data transformations on distributed memory multiprocessors. Through much research, we find the rows in linear data transformation matrices have two different effects on improving locality. Some rows have the effect of optimizing memory locality. They partition data space effectively and put dependent data together to reduce remote memory access overheads. We call these rows as *memory locality optimizing rows* (MLORs). The other rows have the effect of optimizing cache locality. They reshape the access patterns of array references along columns to reduce local memory access overheads (we assume the default memory layout is column-major, but the approach can be applied to row-major memory layout

too). We call these rows as *cache locality optimizing rows* (CLORs). In this paper, we first present a theoretical framework of data space fusion, which is used to partition data space effectively, and determine MLORs based on it. Then under the condition of not affecting memory locality, we use the approach presented in [9] to reshape the access patterns along columns for cache locality and determine CLORs accordingly. At last, we combine MLORs and CLORs to form the final data transformation matrices. The approach can handle not only perfect loop nests but also non-perfect loop nests. It can simultaneously optimize memory and cache locality and can be naturally integrated with data replication and offset alignment. Therefore, our approach can reduce remote and local memory access overheads as much as possible. We conduct experiments with nine programs and the results show our approach is effective.

## 2 Technical Preliminaries

The program model used here is a single perfect or non-perfect loop nest and contains explicit information about which loop can be parallelized. An m-dimensional array X defines an m-dimensional polyhedron, each point of which can be denoted by an  $m\times 1$  column vector. Assume the number of all the loops enclosing a reference of X is n, then the iteration space of this n-deep loop nest can be viewed as an n-dimensional polyhedron where each point is denoted by an  $n\times 1$  column vector  $\overline{I}=(i_1,i_2,\cdots,i_n)^T$ ; here, each  $i_k$  denotes a loop index. We call  $\overline{I}$  as the *iteration vector*. We assume all loop bounds and subscript expressions are affine functions of enclosing loop indices and symbolic constants. Then, the reference can be denoted by  $A\overline{I}+\overline{o}$ ,  $m\times n$  matrix A is called as the *access matrix*, and  $m\times 1$  column vector  $\overline{o}$  is called as the *offset vector* [4]. Moreover, we assume at least one of the loops enclosing each reference of each array can be parallelized.

We use  $span\{\overline{b}_1, \dots, \overline{b}_l\}$  to denote the space spanned by vectors  $\overline{b}_1, \dots, \overline{b}_l$ , Q to denote rational number field,  $Q^n$  to denote the space composed of all the  $n \times 1$  rational number vectors, and  $\dim(\Psi)$  to denote the dimension of vector space  $\Psi$ . We define  $\overline{b} + \Psi = \{\overline{q} | \overline{q} = \overline{b} + \overline{p}, \overline{p} \in \Psi\}$ , where  $\overline{b}$  is an  $n \times 1$  column vector, and  $\Psi$  is a vector space composed of  $n \times 1$  column vectors.

## 3 Memory Locality Optimization

## 3.1 Data Space Decompositions

Given a reference of an m-dimensional array X, we assume the loop indices of all the loops enclosing this reference are  $i_1, \dots, i_n$  from outermost to innermost respectively. Moreover, we assume loops  $i_{p_1}, \dots, i_{p_\nu}$  can be parallelized. We denote the general form of the iteration space decomposition of this n-deep loop nest as

$B_X(i_{p_1},\cdots,i_{p_v})=i_{p_1}\overline{e}_{p_1}+\cdots+i_{p_v}\overline{e}_{p_v}+span\Big\{\overline{e}_{p_{v+1}},\cdots,\overline{e}_{p_n},\overline{0}\Big\}, \text{ where } \overline{e}_{p_j} \text{ is an } n\times 1 \text{ unit column vector. We call } \Big\{B_X(i_{p_1},\cdots,i_{p_v})\Big|i_{p_1},\cdots,i_{p_v}\in Q\Big\} \text{ as a } \text{ linear computation } \text{ decomposition of the iteration space of this } n\text{-deep loop nest and define its } \text{ parallel-ism} \text{ as } v\text{. We also call } B_X(i_{p_1},\cdots,i_{p_v}) \text{ as the } \text{ iteration partition.}$

**Definition 1.** Given an m-dimensional array X, a set of  $m \times 1$  column vectors  $\overline{\delta}, \overline{\gamma}_1, \cdots, \overline{\gamma}_v$ , and a vector space  $\Omega_X$  composed of  $m \times 1$  column vectors. Let  $D_X(k_1, \cdots k_v) = \overline{\delta} + k_1 \overline{\gamma}_1 + \cdots + k_v \overline{\gamma}_v + \Omega_X$  (  $v \ge 0$  ). Assume  $\dim(\Omega_X) = u$  and  $\overline{\eta}_1, \cdots, \overline{\eta}_u$  are a basis of  $\Omega_X$ . If v = 0 or  $v \ne 0$  and  $\forall 1 \le j \le v$ ,  $\overline{\gamma}_j$  can not be expressed as a linear combination of  $\overline{\gamma}_1, \cdots, \overline{\gamma}_{j-1}, \overline{\gamma}_{j+1}, \cdots, \overline{\gamma}_v, \overline{\eta}_1, \cdots, \overline{\eta}_u$ , then we call  $\left\{D_X(k_1, \cdots, k_v) \middle| k_1, \cdots, k_v \in Q\right\}$  as a linear data decomposition of the data space of array X and the parallelism of this linear data decomposition is v. We also call  $D_X(k_1, \cdots k_v)$  as the data partition.

Assume the reference of array X is  $A_X \bar{I}_X + \overline{o}_X$ , where  $\bar{I}_X = (i_1, \cdots, i_n)^T$ , and Let  $\overline{\gamma}_{p_j} = A_X \overline{e}_{p_j}$ , then the data space accessed by iteration partition  $B_X (i_{p_1}, \cdots, i_{p_v})$  is  $D_X (i_{p_1}, \cdots, i_{p_v}) = \overline{o}_X + i_{p_1} \overline{\gamma}_{p_1} + \cdots + i_{p_v} \overline{\gamma}_{p_v} + span \{ \overline{\gamma}_{p_{v+1}}, \cdots, \overline{\gamma}_{p_u}, \overline{0} \}$ .

If  $\forall 1 \leq j \leq v$ ,  $\bar{\gamma}_{p_j}$  can not be expressed as a linear combination of  $\bar{\gamma}_{p_1}, \cdots, \bar{\gamma}_{p_{j+1}}, \cdots, \bar{\gamma}_{p_j}$ , then from definition 1 we know  $\left\{D_X(i_{p_1}, \cdots, i_{p_v}) \middle| i_{p_1}, \cdots, i_{p_v} \in Q\right\}$  is a linear data decomposition of array X's data space and its parallelism is v. As the data partitions accessed by any two different iteration partitions are different, each iteration partition with its accessed data partition can be scheduled to the same processor to make the reference local.

If  $\exists 1 \leq j \leq v$ ,  $\overline{\gamma}_{p_j}$  can be expressed as a linear combination of  $\overline{\gamma}_{p_1}, \cdots, \overline{\gamma}_{p_{j+1}}, \cdots, \overline{\gamma}_{p_{j+1}}, \cdots, \overline{\gamma}_{p_n}$ . Let  $0 \leq v' < v$ . Without loss of generality, we assume  $\forall 1 \leq j \leq v'$ ,  $\overline{\gamma}_{p_j}$  can not be expressed as a linear combination of  $\overline{\gamma}_{p_1}, \cdots, \overline{\gamma}_{p_{j+1}}, \overline{\gamma}_{p_{j+1}}, \cdots, \overline{\gamma}_{p_n}$  while  $\forall v'+1 \leq j \leq v$ ,  $\overline{\gamma}_{p_j}$  can. Let  $D_X'(i_{p_1}, \cdots, i_{p_v}) = \overline{o}_X + i_{p_1} \overline{\gamma}_{p_1} + \cdots + i_{p_v} \overline{\gamma}_{p_v} + span\{\overline{\gamma}_{p_{v+1}}, \cdots, \overline{\gamma}_{p_n}, \overline{0}\}$ , and then  $\left\{D_X'(i_{p_1}, \cdots, i_{p_v}) \middle| i_{p_1}, \cdots, i_{p_v} \in Q\right\}$  is a linear data decomposition of array X 's data space and its parallelism is v'. As  $\forall i_{p_1}, \cdots, i_{p_v} \in Q$ ,  $D_X(i_{p_1}, \cdots, i_{p_v}) \subseteq D_X'(i_{p_1}, \cdots, i_{p_v})$  and v' < v, there exist the circumstances that more than one iteration partition accesses the same data partition, and therefore the data partitions have to be replicated to make the reference local.

**Definition 2.** Given a linear computation decomposition of the iteration space of a loop nest and a linear data decomposition of an array referenced in the loop nest that

is got by the linear computation decomposition, we assume the parallelism of the linear computation decomposition is v and the parallelism of the linear data decomposition is f. Then we call the *replication degree* of the linear data decomposition relative to the linear computation decomposition is v - f.

We always hope the replication degree is as low as possible, because it will make the amount of data needed to be replicated as small as possible and will reduce the runtime overhead of maintaining the consistency of the replicated data.

## 3.2 Data Space Fusion

Given a loop nest with an m-dimensional array X 's q references  $A_{x^j} \bar{I}_{x^j} + \bar{o}_{x^j}$  $(1 \le j \le q)$ , assume  $\bar{I}_{y^j}$  contains  $n_j$  elements and the parallelizable loops enclosing all references of array X are all same. Let the loop indices of these parallelizable loops are  $i_1, \dots, i_v$ .  $\forall 1 \le j \le q$ , we define a position function  $ps_{x^j}$  for  $\bar{I}_{x^j}$ . The definition domain  $\Delta_j$  of  $ps_{\chi^j}$  is composed of all the elements in  $ar{I}_{\chi^j}$ , and  $ps_{\chi^j}$  takes the value of  $1, \dots, n_i$ .  $\forall i \in \Delta_i$ ,  $ps_{x^i}$  returns the position of i in  $\bar{I}_{x^i}$ . Let  $B_{\chi^{j}}(i_{1},\cdots,i_{v})=i_{1}\overline{e}_{ps_{\chi^{j}}(i_{1})}^{j}+\cdots+i_{v}\overline{e}_{ps_{\chi^{j}}(i_{v})}^{j}+span\{\{\overline{e}_{1}^{j},\cdots,\overline{e}_{n_{j}}^{j},\overline{0}\}-\{\overline{e}_{ps_{\chi^{j}}(i_{1})}^{j},\cdots,\overline{e}_{ps_{\chi^{j}}(i_{v})}^{j}\}\}.$ According to Section 3.1, we can know  $\{B_{v_i}(i_1,\dots,i_v)|i_1,\dots,i_v \in Q\}$  is a linear computation decomposition of the iteration space of the  $n_i$ -deep loop nest, which is composed of all the loops enclosing reference  $A_{x^j} \bar{I}_{x^j} + \bar{o}_{x^j}$ . Therefore for each reference of array X, we can use the method presented in Section 3.1 to get the corresponding linear data decomposition of array X 's data space. If q > 1, there will be more than one linear data decomposition of array X 's data space. As the linear data decomposition of X should be unique (for we only consider static data decompositions in the paper and don't consider data redistribution), therefore we have to fuse all those linear data decompositions into a unique one. Assume the fused unique linear data decomposition is  $\left\{D_{X}\left(i_{h_{1}},\cdots,i_{h_{n}}\right)\middle|i_{h_{1}},\cdots,i_{h_{n}}\in Q\right\}$ , where  $0\leq v\leq v$  and  $1 \le h_1, \cdots, h_v \le v$ . Then it should satisfy the condition:  $\forall i_1, \cdots, i_v \in Q, 1 \le j \le q$ , there has  $\overline{o}_{X^j} + A_{X^j} B_{X^j} (i_1, \dots, i_v) \subseteq D_X (i_{h_1}, \dots, i_{h_v})$ . It is possible that many linear data decompositions satisfy the condition, and we want to acquire the one with the highest parallelism, which will make the replication degree the lowest. We give the algorithm of finding the fused unique linear data decomposition that satisfies the condition and has the highest parallelism in Fig. 1.

From the algorithm we can see that as long as the loop indices of the parallelizable loops enclosing all references of given arrays are same, the algorithm can be used to get the fused unique linear data decompositions for these arrays respectively, otherwise we can make them same by aligning parallelizable loops. As the limitation of the

Input: a loop nest with array X 's q references  $A_{\chi^1} \bar{I}_{\chi^1} + \overline{o}_{\chi^1}, \cdots, A_{\chi^q} \bar{I}_{\chi^q} + \overline{o}_{\chi^q}$ . The parallelizable loops enclosing all references of array X are all same. Output: array X 's fused unique linear data decomposition. Assume  $\bar{I}_{v^j}$  contains  $n_i$  elements, the loop indices of these parallelizable loops are  $i_1, \dots, i_v$ and  $\bar{\gamma}_{ik}$  is the k th column of  $A_{x^j}$ , where  $1 \le j \le q, 1 \le k \le n_j$ .  $\theta = \{\overline{0}\};$ DO j = 1, q $\theta = \theta \cup (\{\overline{\gamma}_{j1}, \dots, \overline{\gamma}_{jn_i}\} - \{\overline{\gamma}_{j(ps_{-i}(i_i))}, \dots, \overline{\gamma}_{j(ps_{-i}(i_v))}\})$ **ENDDO** DO j = 2, qDO k = 1, v $\theta = \theta \cup \{\overline{\gamma}_{i(ps_{-1}(i_k))} - \overline{\gamma}_{1(ps_{-1}(i_k))}\}$ **ENDDO ENDDO** DO j = 2, q $\theta = \theta \cup \{\overline{o}_{v_i} - \overline{o}_{v_i}\}$ **ENDDO**  $\Omega_{X} = span\{\theta\}; \ D_{X}(i_{1}, \dots, i_{v}) = \overline{o}_{X^{1}} + i_{1}\overline{\gamma}_{1(ps_{v^{1}}(i_{1}))} + \dots + i_{v}\overline{\gamma}_{1(ps_{X^{1}}(i_{v}))} + \Omega_{X};$

Let  $0 \leq v^{'} \leq v$ , without loss of generality, assume  $\forall 1 \leq j \leq v^{'}$ ,  $\overline{\gamma}_{1(ps_{\chi^{1}}(i_{j}))}$  can not be expressed as a linear combination of  $\overline{\gamma}_{1(ps_{\chi^{1}}(i_{j}))}, \cdots, \overline{\gamma}_{1(ps_{\chi^{1}}(i_{j-1}))}, \overline{\gamma}_{1(ps_{\chi^{1}}(i_{j+1}))}, \cdots, \overline{\gamma}_{1(ps_{\chi^{1}}(i_{j}))}, \overline{\eta}_{1}, \cdots, \overline{\eta}_{u}$ , while

$\forall v'+1 \leq j \leq v \ , \quad \overline{\gamma}_{1(ps_{x^1}(i_j))} \quad \text{can;} \quad \text{let} \quad \Omega_X' = span\{\Omega_X \cup \{\overline{\gamma}_{1(ps_{x^1}(i_{v+1}))}, \cdots, \overline{\gamma}_{1(ps_{x^1}(i_v))}\}\} \quad \text{and} \quad D_X'(i_1, \cdots, i_{v'}) = \overline{o}_{x^1} + i_1\overline{\gamma}_{1(ps_{x^1}(i_v))} + \cdots + i_{v'}\overline{\gamma}_{1(ps_{x^1}(i_v))} + \Omega_X';$

Return  $(\{D_X(i_1,\dots,i_{v'})|i_1,\dots,i_{v'}\in Q\})$

Let  $\dim(\Omega_x) = u$  and  $\overline{\eta}_1, \dots, \overline{\eta}_u$  are a basis of  $\Omega_x$ ;

Fig. 1. The algorithm of finding the fused unique linear data decomposition

space, the detailed steps of the alignment of parallelizable loops are omitted here. In the following discussions, we assume the loop indices of the parallelizable loops enclosing all references of all arrays are same.

## 3.3 Determining Memory Locality Optimizing Rows

Given an m-dimensional array X 's multiple references, let array X 's fused unique linear data decomposition gotten by the algorithm given in Fig. 1. is  $\left\{D_X(i_1,\cdots,i_\nu)=\overline{o}_X+i_1\overline{\gamma}_1+\cdots+i_\nu\overline{\gamma}_\nu+\Omega_X\left|i_1,\cdots,i_\nu\in Q\right.\right\}$ . The parallelism of this linear data decomposition is  $\nu$ . We determine the MLORs for X in the following.

If v = 0, array X has to be replicated over all dimensions of the processor space to make all the accesses to X local. Therefore, we determine X 's MLORs are null. In the following, we will discuss the circumstance of  $v \neq 0$ .

Assume  $\dim(\Omega_X)=u$  and  $\overline{\eta}_1,\cdots,\overline{\eta}_u$  are a basis of  $\Omega_X$ . If u+v< m, we add m-u-v column vectors  $\overline{\eta}_{u+1},\cdots,\overline{\eta}_{m-v}$  to make  $\overline{\gamma}_1,\cdots,\overline{\gamma}_v,\overline{\eta}_1,\cdots,\overline{\eta}_{m-v}$  a basis of  $Q^m$ . Let  $\Omega_X'=span\{\overline{\eta}_1,\cdots,\overline{\eta}_{m-v},\overline{0}\}$ . We can find an orthogonal basis of  $\Omega_X'$  's orthogonal space, which is assumed as  $\overline{\beta}_1,\cdots,\overline{\beta}_v$ . Assume  $\overline{\gamma}_k=z_{k1}\overline{\beta}_1+\cdots+z_{kv}\overline{\beta}_v+z_{k(v+1)}\overline{\eta}_1+\cdots+z_{km}\overline{\eta}_{m-v}$ . Let  $C=(\overline{\beta}_1,\cdots,\overline{\beta}_v)$ ,  $P=\begin{pmatrix}1/\||\overline{\beta}_1|\|^2&\cdots&0\\ \vdots&\ddots&\vdots\\0&\cdots&1/\||\overline{\beta}_v\|\|^2\end{pmatrix}$ ,  $P=\begin{pmatrix}z_{11}&\cdots&z_{v1}\\\vdots&\ddots&\vdots\\z_{1v}&\cdots&z_{vv}\end{pmatrix}$  and  $\overline{d}_j$  be the jth row of

$H^{-1}P(C)^T$ .  $\forall 1 \leq j \leq v$ , we multiply  $\overline{d}_j$  by a smallest positive integer to make all the elements in  $\overline{d}_j$  become integers, and we finally determine array X's MLORs are  $\overline{d}_1, \cdots, \overline{d}_v$  and the offset needed by the affine data transformation is  $\overline{o}_X$ .

## 4 Cache Locality Optimization and the Determination of the Final Linear Data Transformation Matrices

We use the approach presented in [9] to optimize cache spatial locality and continue to use the notations used in Section 3.3 in the following discussion. Given a reference of array X, assume the innermost loop index occurring in the subscript expressions of this reference is  $\zeta$ . Without loss of generality, we determine the CLORs and the final linear data transformation matrix N for this reference in the following.

- 1. if v=0, use the approach presented in [9] to find the data transformation matrix M that can optimize the spatial locality of this reference. Let the rows of M from the first to the last be  $\overline{\rho}_1, \dots, \overline{\rho}_m$  respectively. We then determine  $\overline{\rho}_1, \dots, \overline{\rho}_m$  are the CLORs and N's rows from the first to the last are  $\overline{\rho}_1, \dots, \overline{\rho}_m$  respectively with its corresponding affine data transformation Nx.

- 2. if  $v \neq 0$  and  $\forall 1 \leq j \leq v$ ,  $\zeta \neq i_j$ , find m-v integer row vectors  $\overline{b}_1, \dots, \overline{b}_{m-v}$  to make  $(\overline{d}_1)^T, \dots, (\overline{d}_v)^T, (\overline{b}_1)^T, \dots, (\overline{b}_{m-v})^T$  a basis of  $Q^m$  and use them to compose a non-singular square matrix E, where its first m-v rows from the first to the last are  $\overline{b}_1, \dots, \overline{b}_{m-v}$  respectively and its last v rows are  $\overline{d}_1, \dots, \overline{d}_v$ . Use  $E(x-\overline{o}_x)$  to do affine transformation on the reference and let  $\varpi$  be the array composed of the first m-v dimensions of the transformed reference. We use the approach presented in [9] to find the  $(m-v)\times (m-v)$  non-singular data transformation matrix R that can

optimize the spatial locality of array  $\varpi$ . Let  $M = R \Big( (\overline{b}_1)^T \cdots (\overline{b}_{m-v})^T \Big)^T$ , and the rows of M from the first to the last be  $\overline{\rho}_1,\cdots,\overline{\rho}_{m-\nu}$  respectively. We determine  $\overline{\rho}_1,\cdots,\overline{\rho}_{\scriptscriptstyle m-\nu}$  are the CLORs and N 's rows from the first to the last are  $\overline{\rho}_1,\cdots,\overline{\rho}_{\scriptscriptstyle m-\nu}$ ,  $\overline{d}_1, \dots, \overline{d}_v$  respectively with its corresponding affine data transformation  $N(x-\overline{o}_x)$ . 3. if  $v \neq 0$  and  $\exists 1 \leq j \leq v$ ,  $\zeta = i_j$ , find m - v integer row vectors  $\overline{b_1}, \dots, \overline{b_{m-v}}$  to make  $(\overline{d}_1)^T, \dots, (\overline{d}_v)^T, (\overline{b}_1)^T, \dots, (\overline{b}_{m-v})^T$  a basis of  $Q^m$  and use them to compose a non-singular square matrix E, where its first m-v+1 rows from the first to the last are  $\overline{d}_i, \overline{b}_1, \dots, \overline{b}_{m-v}$  respectively and its last v-1 rows are  $\overline{d}_1, \dots, \overline{d}_{i-1}, \overline{d}_{i+1}, \dots, \overline{d}_v$ . Use  $E(x-\overline{o}_x)$  to do affine transformation on the reference and let  $\varpi$  be the array composed of the first m-v+1 dimensions of the transformed reference. We use the approach presented in [9] to find the  $(m-v+1)\times(m-v+1)$  non-singular data transformation matrix that can optimize the spatial locality of array  $\varpi$  , and get matrix Rby replacing the first row of the above data transformation matrix with a  $1 \times (m-v+1)$  row vector where its first element is numeral one and all the others are zeros. Let  $M = R((\overline{d}_j)^T (\overline{b}_1)^T \cdots (\overline{b}_{m-\nu})^T)^T$ , and the rows of M from the second to the last be  $\overline{\rho}_1,\cdots,\overline{\rho}_{m-\nu}$  respectively. We determine  $\overline{d}_j,\overline{\rho}_1,\cdots,\overline{\rho}_{m-\nu}$  are the CLORs and N 's rows from the first to the last are  $\overline{d}_i, \overline{\rho}_1, \dots, \overline{\rho}_{m-v}$  $\overline{d}_1, \dots, \overline{d}_{i-1}, \overline{d}_{i+1}, \dots, \overline{d}_v$  respectively with its corresponding affine data transformation  $N(x-\overline{o}_x)$ . In this circumstance,  $\overline{d}_i$  is both the MLOR and the CLOR.

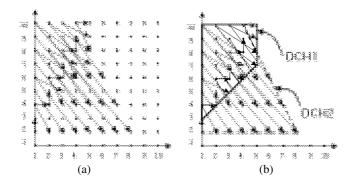

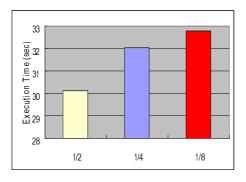

## 5 Experimental Results

We will present performance results for the following nine programs: *matmult* is a matrix-multiplication routine; syr2k is a banded matrix update routine from BLAS; stencil is a five-point stencil computing code; htribk is a test program from Eispack; mxm, cholsky and cfft2d1 are three test programs from Spec92/NASA benchmark suite; mxmxm is a routine from [10] that multiplies three matrices; transpose is a routine from a large computational chemistry application [13]. We conduct experiments with FORTRAN versions of these programs. For each program, we experiment with four different versions: the version with parallelization analysis only (denoted by 0); the version with parallelization analysis and memory locality optimization using the method presented in Section 3 (denoted by 0+m); the version with parallelization analysis and cache locality optimization using the approach presented in [9] (denoted by 0+c); and the version with parallelization analysis and memory and cache locality optimization using the approach presented in this paper (denoted by 0+mc).

We report speedups for up to 64 processors on some distributed memory machine. This machine has 32 nodes and each node has two processors. Shared memory architecture is adopted inside each node while distributed memory architecture is adopted among nodes. Table 1 gives speedups of the test programs in different versions.

| nn | matmult |      |      | syr2k |      |      |      | stencil |      |      |      |      |

|----|---------|------|------|-------|------|------|------|---------|------|------|------|------|

| pn | О       | o+m  | o+c  | o+mc  | 0    | o+m  | o+c  | o+mc    | 0    | o+m  | o+c  | o+mc |

| 2  | 1.69    | 1.66 | 24.3 | 25.4  | 3.27 | 2.15 | 35.6 | 40.3    | 1.20 | 1.27 | 5.34 | 7.39 |

| 4  | 3.32    | 3.32 | 46.5 | 50.4  | 6.39 | 4.26 | 57.3 | 75.8    | 2.09 | 2.40 | 6.20 | 12.5 |

| 8  | 6.61    | 6.63 | 84.9 | 101   | 11.9 | 8.38 | 69.6 | 136     | 2.97 | 4.26 | 5.79 | 22.7 |

| 16 | 12.9    | 12.9 | 134  | 201   | 19.1 | 16.3 | 57.3 | 224     | 2.91 | 7.14 | 3.96 | 33.9 |

| 32 | 24.4    | 25.5 | 151  | 394   | 25.1 | 31.2 | 45.6 | 322     | 2.33 | 10.9 | 2.69 | 43.5 |

| 64 | 40.5    | 49.8 | 128  | 544   | 22.2 | 58.6 | 27.6 | 427     | 1.52 | 14.9 | 1.59 | 50.7 |

**Table 1.** The speedups of the test programs in different versions

| nn | htribk |      |      | mxm  |      |      |      | cholsky |      |      |      |      |

|----|--------|------|------|------|------|------|------|---------|------|------|------|------|

| pn | О      | o+m  | o+c  | o+mc | 0    | o+m  | o+c  | o+mc    | 0    | o+m  | o+c  | o+mc |

| 2  | 1.89   | 1.91 | 11.3 | 11.5 | 2.05 | 2.03 | 10.9 | 10.1    | 0.17 | 2.23 | 0.24 | 12.2 |

| 4  | 3.64   | 3.69 | 19.5 | 28.5 | 4.05 | 4.03 | 15.7 | 19.9    | 0.13 | 4.30 | 0.15 | 21.1 |

| 8  | 7.65   | 7.84 | 58.5 | 82.3 | 7.68 | 8.14 | 27.5 | 44.2    | 0.08 | 7.03 | 0.09 | 33.1 |

| 16 | 13.6   | 12.4 | 63.1 | 161  | 13.3 | 15.9 | 38.4 | 84.7    | 0.04 | 10.1 | 0.05 | 46.2 |

| 32 | 17.0   | 23.8 | 49.3 | 302  | 18.8 | 31.3 | 37.0 | 156     | 0.02 | 15.5 | 0.02 | 57.8 |

| 64 | 18.4   | 44.9 | 26.5 | 514  | 18.0 | 59.8 | 21.9 | 289     | 0.01 | 28.9 | 0.01 | 57.8 |

| nn | cfft2d1 |      |      | mxmxm |      |      |      | transpose |      |      |      |      |

|----|---------|------|------|-------|------|------|------|-----------|------|------|------|------|

| pn | О       | o+m  | o+c  | o+mc  | О    | o+m  | o+c  | o+mc      | О    | o+m  | o+c  | o+mc |

| 2  | 0.27    | 3.32 | 0.72 | 3.32  | 8.07 | 2.07 | 26.6 | 27.4      | 0.50 | 1.47 | 0.71 | 11.8 |

| 4  | 0.24    | 4.39 | 0.50 | 4.24  | 5.90 | 4.03 | 49.2 | 54.6      | 0.57 | 2.81 | 0.69 | 23.5 |

| 8  | 0.19    | 5.59 | 0.30 | 5.59  | 8.83 | 8.24 | 82.7 | 108       | 0.52 | 5.05 | 0.56 | 41.7 |

| 16 | 0.13    | 6.47 | 0.17 | 9.46  | 14.9 | 16.2 | 108  | 212       | 0.38 | 9.00 | 0.39 | 92.2 |

| 32 | 0.07    | 7.23 | 0.09 | 15.4  | 30.1 | 32.3 | 108  | 412       | 0.24 | 14.0 | 0.24 | 179  |

| 64 | 0.04    | 7.23 | 0.05 | 20.5  | 39.2 | 64.6 | 75.3 | 761       | 0.12 | 19.8 | 0.13 | 342  |

pn denotes processor number. [matmult-2048×2048 matrices; syr2k-1024×1024 matrices; stencil-2048×2048 matrices; htribk-1024×1024 matrices; mxm-1024×1024 matrices; cholsky-the size parameters are set to 1000; cfft2d1-1024×1024 matrices and 2×1024 arrays; mxmxm-1024×1024 matrices; transpose-4096×4096 matrices]

As the o versions have not been optimized for memory and cache locality, their performance is bad for high remote and local memory access overheads. As the o+m versions have been optimized for memory locality, the remote memory access overheads will be low. But as they have not been optimized for cache locality, high local memory access overheads may prevent their performance from improving further. Although the o+c versions have been optimized for cache locality to make local memory access overheads low, there may exist high remote memory access overheads for bad memory locality. Moreover, the remote memory access overheads may increase with the increase of processor number. When the negative effect of remote memory access overheads on the performance exceeds the positive effect of cache locality optimization, the performance will get worse instead. As the o+mc versions have been optimized for memory and cache locality simultaneously, there will be low remote and local memory access overheads and therefore their performance should be better than the other three versions' performance. From Table 1 we can see that in all nine programs, the o+mc versions' performance is the best in four versions and for most of the nine programs, with the increase of processor number, the gap of optimizing effect between the o+mc versions and the other three versions becomes larger.

## 6 Conclusions

To solve the problems of memory and cache locality optimization on distributed memory multiprocessors, we present an approach of optimizing memory and cache locality simultaneously using data transformations in this paper. We first determine MLORs for memory locality, then determine CLORs for cache locality and combine MLORs and CLORs in some order to form the final linear data transformation matrices that can optimize memory and cache locality simultaneously at last. The experimental results show our approach is effective on distributed memory multiprocessors.

#### References

- 1. T.-S. Chen and C.-Y. Chang. Skewed data partition and alignment techniques for compiling programs on distributed memory multicomputers. The Journal of Supercomputing, 21(2): 191-211, 2002.

- W.-L. Chang, C.-P. Chu and J.-H. Wu. Communication-free alignment for array references with linear subscripts in three loop index variables or quadratic subscripts. The Journal of Supercomputer, 20(1): 67-83, 2001.

- XIA Jun, YANG Xue-Jun and DAI Hua-Dong. Data space fusion based approach for effective alignment of computation and data. In Proc. of 5th International Workshop on Advanced Parallel Processing Technology, Xiamen, China, pp. 215-225, 2003.

- M. Wolf and M. Lam. A data locality optimizing algorithm. In SIGPLAN91 Conference on Programming Language Design and Implementation, Toronto, Canada, pp. 30-44, 1991.

- K. McKinley, S. Carr and C.W. Tseng. Improving data locality with loop transformation. ACM Transactions on Programming Languages and Systems, 18(4): 424-453, 1996.

- A.J.C. Bik and P.M.W. Knijnenburg. Reshaping Access Patterns for Improving Data Locality. In Proc. of 6th Workshop on Compilers for Parallel Computers, 1996.

- P. Clauss and B. Meister. Automatic memory layout transformations to optimize spatial locality in parameterized loop nests. ACM SIGARCH Computer Architecture News, 28(1): 11-19, 2000.

- M. Kandemir, A. Choudhary, N. Shenoy, P. Banerjee and J. Ramanujam. A hyperplane based approach for optimizing spatial locality in loop nests. In Proc. of 1998 ACM International Conference on Supercomputing (ICS'98), Melbourne, Australia, pp. 69-76, 1998.

- XIA Jun, YANG Xue-Jun, ZENG Li-Fang and ZHOU Hai-Fang. A projectiondelamination based approach for optimizing spatial locality in loop nests. Chinese Journal of Computers, 26(5):539-551, 2003.

- M. Cierniak and W. Li. Unifying data and control transformations for distributed shared memory machines. In SIGPLAN95 Conference on Programming Language Design and Implementation, La Jolla, CA, pp. 205-217, 1995.

- M. Kandemir, A. Choudhary, J. Ramanujam and P. Banerjee. A matrix-based approach to global locality optimization. Journal of Parallel and Distributed Computing, 58:190-235, 1999.

- M. Kandemir, P. Banerjee, A. Choudhary, J. Ramanujam and E. Ayguade. Static and dynamic locality optimizations using integer linear programming. IEEE Transactions on Parallel and Distributed Systems, 12(9): 922-940, 2001.

- 13. High Performance Computational Chemistry Group. NWChem: A computational chemistry package for parallel computers, version 1.1. Pacific Northwest Laboratory, 1995.

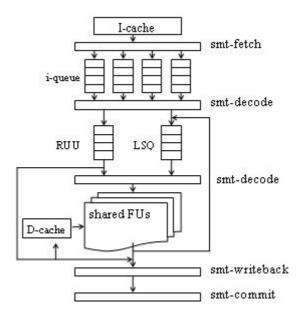

## A Fetch Policy Maximizing Throughput and Fairness for Two-Context SMT Processors

Caixia Sun, Hongwei Tang, and Minxuan Zhang

College of Computer, National University of Defense Technology, Changsha 410073, Hunan, P.R. China {cxsun\_nudt, hwtang\_nudt}@yahoo.com.cn mxzhang@nudt.edu.cn

**Abstract.** In Simultaneous Multithreading (SMT) processors, co-scheduled threads share the processor's resources, but at the same time compete for them. A thread missing in L2 cache may hold a large number of resources which other threads could be using to make forward progress. And as a result, the overall performance of SMT processors is degraded. Currently, many instruction fetch policy focus on this problem. However, these policies are not perfect, and each has its own disadvantages. Especially, these policies are designed for processors implementing any ways simultaneous multithreading. The disadvantages of these policies may become more serious when they are used in two-context SMT processors.

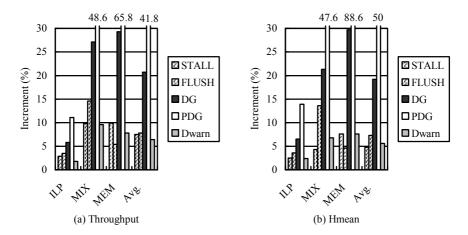

In this paper, we propose a novel fetch policy called RG-FP (Resource Gating based on Fetch Priority), which is specially designed for two-context SMT processors. RG-FP combines reducing fetch priority with controlling shared resource allocation to prevent the negative effects caused by loads missing in L2 cache. Simulation results show that our RG-FP policy outperforms previously proposed fetch policies for all types of workloads in both throughput and fairness, especially for memory bounded workloads. Results also tell that our policy shows different degrees of improvement over other fetch policies. The increment over PDG is greatest, reaching 41.8% in throughput and 50.0% in Hmean on average.

#### 1 Introduction

Simultaneous Multithreading (SMT) processors [1,2,3] improve performance by allowing running instructions from several threads simultaneously at a single cycle. Co-scheduled threads share some resources, such as issue queues, physical registers, and functional units. The way of allocating shared resources among the threads will affect the overall performance of SMT processors. Currently, shared resources allocation in SMT processors is dynamically decided by the instruction fetch policy.

In SMT processors, the number of shared resources is limited, so if a thread holds critical resources for a long time, other threads may run slower than they could or even stall because of lack of resources. A load missing in L2 cache usually causes this

happen. Many instruction fetch policies have been proposed to address this problem, some of which are well known, such as STALL, FLUSH [4], DG and PDG [5]. A newly proposed fetch policy called DWarn [6] is also very efficient to handle L2 cache misses. However, these policies are not perfect, and each has its own disadvantages. Especially, these policies are very general, that is to say, they are designed for processors implementing any ways simultaneous multithreading. The disadvantages of these policies may become more serious when being used in two-context SMT processors. For example, FLUSH deallocates all the resources allocated to the thread with L2 cache misses and makes them available to the other threads. It will produce resource under-use when the resources deallocated are not required by any other thread. For two-context SMT processors, the pressure on shared resources is not high, so resource under-use will be more serious.

It is well known that many commercial processors implement two-way simultaneous multithreading, like Intel Xeon [7] and IBM Power5 [8]. Furthermore, in SMT processors with more than two hardware contexts, it is very common that only two threads are running together because there are not enough thread-level parallelisms. Therefore, we believe it is very important to specially design a fetch policy for two-context SMT processors. Certainly, when there are more than two hardware contexts, such a fetch policy can also be combined with other policies to achieve better performance.

In this paper, we propose a novel fetch policy called RG-FP, which is specially used in two-context SMT processors. RG-FP is built on top of ICOUNT, and combines reducing fetch priority with controlling shared resource allocation to prevent the effects of loads that miss in L2 cache. In out policy, a thread with cache misses would not be stalled immediately, but executes at a lower fetch priority. Thus, resource underutilization and idle cycles are reduced greatly. Furthermore, resources are allocated between threads based on the fetch priority, and a thread with cache misses will be gated when it attempts to exceed its assigned resources. In this way, we can prevent resource monopolization.

This paper is organized as follows. Section 2 introduces the related work. In Section 3 we detail our policy. Sections 4 and 5 present the methodology and the results. Finally, concluding remarks are given in Section 6.

## 2 Related Work

ICOUNT [2] prioritizes threads with few instructions in decode, rename, and the instruction queues. It presents good results for threads with high ILP(Instruction Level Parallelism). However, ICOUNT could not address the problems caused by L2 cache misses. As long as the fetch priority of a thread is the highest, ICOUNT will fetch instructions from this thread, even if this thread is experiencing L2 cache misses. The reason that we introduce ICOUNT here is the following policies that handle L2 cache misses are all based on it.

STALL [4] attempts to prevent the threads with L2 cache misses occupying most of available resources. It detects that a thread has a pending L2 miss and stalls fetch-

ing from this thread to avoid resource abuse. However, L2 miss detection may be so late that shared resources have been clogged. Furthermore, it is possible that the resources allocated to a thread are not required by any other thread, so stalling fetching from this thread will produce resource under-use. Obviously, for two-context SMT processors, it is easier to cause resource abuse or produce resource under-use.

FLUSH [4] is an extension of STALL. It tries to correct the case in which an L2 miss is detected too late by deallocating all the resources of the offending thread, making them available to the other executing threads. However, compared to STALL, it is more likely to produce resource under-use for FLUSH. Furthermore, extra fetch and power are required to redo the work for the flushed thread. For two-context SMT processors, the pressure on shared resources is not high, so resource under-use will be more serious.

Data Gating (DG) [5] attempts to reduce the effects of loads missing in the L1 data cache by stalling threads on each L1 data miss. However, there is not resource abuse when an L1 miss does not cause an L2 miss. Thus, to stall a thread every time it experiences an L1 miss may be too severe. For two-context SMT processors, another problem is that it is very easy to produce idle cycles, because the probability of two threads simultaneously experiencing L1 cache misses is high.

Predictive Data Gating (PDG) [5] works like STALL, that is, it prevents a thread from fetching instructions as soon as a cache miss is predicted. By using a miss predictor, they avoid detecting the cache miss too late, but resource under-use still exists. Furthermore, cache misses prove to be hard to predict accurately [9]. Like DG, it is also very easy to produce idle cycles for two-context SMT processors.

DCache Warn (DWarn) [6] uses a hybrid mechanism. When less than two threads run, the priority of the thread missing in L1 data cache miss is reduced. After that, if the L1 miss turns to an L2 miss, its thread is gated. When the number of execution threads is higher than 2, DWarn only reduces the priority of the threads with cache misses. For two-context SMT processors, the problem of DWarn is there exist idle cycles of the processor when two threads are all gated. Furthermore, although the fetch priority of threads with cache misses is reduced, these threads are stalled until L2 miss is declared, which may still be too late to prevent shared resources being clogged.

The main problems of fetch policies previously introduced are summed up as follows: First, not to effectively prevent shared resources being monopolized by threads with pending L2 misses; Second, to produce resource under-use when preventing a thread occupying resources which are not required by any other thread; Third, to produce idle cycles of the processor when all threads are stalled because of cache misses; Fourth, the most important one, the three problems above may become more serious when these policies are used in two-context SMT processors.

## 3 RG-FP Fetch Policy

RG-FP is specially designed for two-context SMT processors. It attempts to prevent the effects of loads that miss in L2 cache, and at the same time to avoid the problems of the fetch policies above.

#### 3.1 Basic Idea

RG-FP is built on top of ICOUNT. Furthermore, it is based on the combination of two ideas, namely, reducing fetch priority and controlling shared resources allocation.

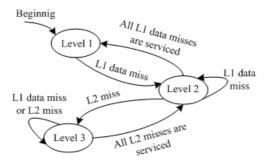

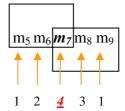

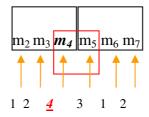

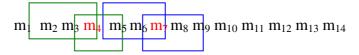

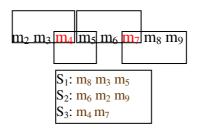

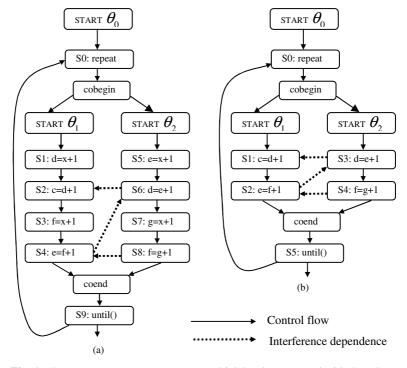

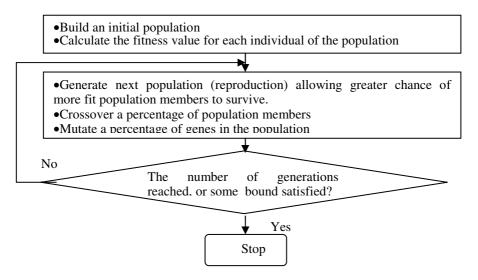

**Reducing Fetch Priority.** RG-FP supports three priority levels for each thread, from Level 1 to Level 3. Level 1 is the highest and Level 3 is the lowest. At the beginning, all threads are at the highest priority, Level 1. If a thread is experiencing an L1 data cache miss, its fetch priority is reduced to Level 2. After that, if the L1 cache misses finally turns to an L2 cache miss, the fetch priority of the thread is reduce further to Level 3. The transition of fetch priority is detailed in Figure 1. The threads at the same priority level are sorted by ICOUNT.

**Fig. 1.** Transition of the fetch priority

**Controlling Shared Resource Allocation.** The number of resources allocated to threads with cache misses is restricted to a certain value and threads with no outstanding cache misses can use as many resources as that are available. If a thread with cache misses is exceeding its assigned resources, it is gated until it releases some of the allocated resources or it is allowed to occupy more resources.

By reducing the fetch priority of threads with cache misses instead of stalling fetching from them, on one hand, the opportunity of keeping the fetch bandwidth fully used is given the thread with no outstanding cache misses, which implies the improvement of throughput; on the other hand, threads with pending cache misses are not stalled, so resource under-use and idle cycles of the processor are reduced greatly.

However, resources monopolization may still happen if we only reduce the fetch priority. Therefore, the idea of controlling resource allocation [10] is added to our policy. Because the resources allocated to threads with cache misses are limited, it is impossible that shared resources are monopolized by these threads. Furthermore, controlling resource allocation between threads may achieve a better throughput-fairness balance [10,11].

#### 3.2 Resource Allocation Mechanism

We can use two methods to allocate shared resources between threads: static resource allocation (SRA) and dynamic resource allocation (DRA). In our simulations, we

implement these two methods respectively. In the rest of this paper, we call RG-FP using static resource allocation RG-FP-S, and RG-FP using dynamic resource allocation RG-FP-D.

In static resource allocation, the number of resources allocated to threads at Level 2 and Level 3 is fixed, all equal to T divided by N, where T is the total number of some resource and N is the number of running threads. Because we only talk about two-context SMT processors, N is two.

In dynamic resource allocation, shared resources are dynamically allocated to threads based on each thread's fetch priority. The number of some resource allocated to thread i (i=0, 1)  $M_i$  is given in the equation (1), where T is the total number of some resource and  $PL_i$  is the fetch priority level of thread i.

$$M_i = \frac{PL_i}{PL_i + PL_{1-i}} *T \tag{1}$$

Table 1 shows an example of the resource allocation for all cases. We can see that in static resource allocation, the thread with cache misses can only occupy one half of some resource at most. In dynamic resource allocation, the thread with lower priority can borrow resources from the thread with higher priority, and as a result, the former can use the resources not required by the latter to reduce resource under-use.

**Table 1.** Resource allocation values for a 32-entry resource. "-" represents the thread can use as many resources as that are available.

|        |        | SF    | RA    | DI    | RA    |

|--------|--------|-------|-------|-------|-------|

| $PL_0$ | $PL_1$ | $M_0$ | $M_1$ | $M_0$ | $M_1$ |

| 1      | 1      | -     | -     | -     | -     |

| 1      | 2      | -     | 16    | -     | 21    |

| 1      | 3      | -     | 16    | -     | 24    |

| 2      | 1      | 16    | -     | 21    | -     |

| 2      | 2      | 16    | 16    | 16    | 16    |

| 2      | 3      | 16    | 16    | 13    | 19    |

| 3      | 1      | 16    | -     | 24    | -     |

| 3      | 2      | 16    | 16    | 19    | 13    |

| 3      | 3      | 16    | 16    | 16    | 16    |

#### 3.3 Implementation

To implement RG-FP, each thread requires two cache miss counters, which are used to track L1 data misses L2 misses respectively, and 5 resources usage counters. Each instruction occupies an active list entry and maybe a physical register before committing. It uses an entry in the issue queues if its operands are not ready, and also require a functional unit. But each thread can have its own active list and functional units are pipelined. Therefore we only need to restrict the usage of issues queues and physical registers by threads with cache misses. There are three kinds of issue queues: integer, fp and load/store, so each thread requires three issue queues usage counters. Two more resource usage counters are required to track physical registers (integer and fp) per thread. The additional complexity required to introduce these counters depends on

the particular implementation, but we do not expect it to be more complex than other hardware counters already present in most processors [10].

L1 data miss counters are incremented every time a thread experiences an L1 cache miss and decremented when the data caches fill occurs. L2 miss counters are incremented every time an L1 miss turns to an L2 miss and decremented when L2 cache fill occurs. If the L2 miss counter of a thread is nonzero, this thread is at Level 3, otherwise if the L1data miss counter is nonzero, it is at Level 2. Only when the L1 data miss counter and the L2 miss counter are all zero, is the thread at Level 1. Issue queues usage counters are incremented in the decode stage and decremented when an instructions is issued for execution. Physical registers usage counters are incremented in the decode stage and decremented in the decode stage and decremented in the commit stage.

In RG-FP, we use ICOUNT2.8 as the basic fetch policy. Each cycle, RG-FP fetches as many instructions as possible from the thread with higher priority, then fill in with instructions from the other thread, up to eight totally. If a thread at Level 2 or Level 3 is allocating more resources, it is fetch-stalled.

Now, we concern how to implement resource allocation between threads. For SRA, the number of resources allocated threads with cache misses is fixed, so extra circuit is not needed. For DRA, simple control logic is needed. DRA can be implemented in two ways. One is using combinational circuit to implement equation (1). The inputs of this circuit include fetch priority of each thread and the total number of some resource. This circuit gives the number of resources allocated to each thread with cache misses. The second way is using a direct-mapped table indexed by fetch priority of each thread. This table has 9 entries, as shown in Table 1. By searching this table, we can acquire the number of resources allocated to each thread with cache misses.

## 4 Methodology

Table 2 summarizes the benchmarks used in our simulations. All benchmarks are taken from the SPEC2000 suite [12] and use the reference data sets as inputs. It is time-consuming to simulate the complete SPEC benchmark suit. So we follow the idea proposed in [13] to run the most representative 300 million instruction segment of each benchmark. Benchmarks are divided into two groups based on their cache behaviors: those experiencing between 0.02 and 0.12 L2 cache misses per instruction, on average, over the simulated portion of the code are considered memory-intensive applications, and the rest have lower miss rates and higher inherent ILP. Table 3 lists the multithreaded workloads used in our simulations. All of the simulations in this paper either contain threads all from the first group (the MEM workloads in Table 3), or all from the second group (ILP), or an equal mix from each group (MIX).

Execution is simulated on an out-of-order superscalar processor model derived from SMTSIM [14]. The simulator models all typical sources of latency, including caches, branch mispredictions, TLB (Translation Lookaside Buffer) misses, etc. It also carefully models execution down the wrong path between branch misprediction and branch misprediction recovery. The baseline configuration of our simulator is shown in Table 4.

Table 2. Benchmarks used

| Type | Benchmark                                        |

|------|--------------------------------------------------|

| MEM  | mcf, twolf, vpr, parser, ammp, applu, art, swim  |

| ILP  | aspi, fma, eon, gcc, gzip, vortex, crafty, bzip2 |

Table 3. Multithreaded Workloads used

| Type | Applications                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------|

| ILP  | {gzip, bzip2}, {gcc, aspi}, {vortex, fma}, {eon, crafty}, {gzip, vortex},                                         |

|      | {aspi, bzip2}, {gcc, crafty}, {fma, eon}                                                                          |

| MIX  | {gzip, vpr}, {gcc, ammp}, {art, vortex}, {fma, parser}, {aspi, twolf}, {crafty, art}, {bzip2, swim}, {eon, applu} |

| MEM  | {mcf, vpr}, {ammp, parser}, {twolf, art}, {mcf, swim}, {vpr, applu},                                              |

|      | {ammp, art}, {parser, twolf}, {swim, applu}                                                                       |

Table 4. Baseline configuration of the simulator

| Parameter                   | Value                                           |

|-----------------------------|-------------------------------------------------|

| Fetch Width                 | 8 instructions per cycle                        |

| Basic Fetch Policy          | ICOUNT2.8                                       |

| Instruction Queues          | 32 int, 32 fp, 32 load/store                    |

| Functional Units            | 6 int, 3 fp, 4 load/store                       |

| Renaming Physical Registers | 100 int, 100 fp                                 |

| Active List Entries         | 256 per thread                                  |

| Branch Predictor            | 2K gshare                                       |

| Branch Target Buffer        | 256 entries, 4-way associative                  |

| RAS                         | 256 entries                                     |

| L1I cache, L1D cache        | 64KB, 2-way, 64-bytes lines, 1 cycle access     |

| L2 cache                    | 512KB, 2-way, 64-bytes lines, 10 cycles latency |

| Main Memory Latency         | 100 cycles                                      |

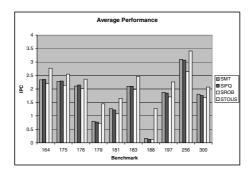

We use two metrics to make a fair comparison: IPC and the Harmonic Mean (Hmean). Just as stated in [4], IPC may be a questionable metric if a fetch policy favors high IPC threads. Hmean is the harmonic mean of the relative IPC of the threads in a workload and it attempts to avoid artificial improvements achieved by giving more resources to threads with high ILP.

#### 5 Results

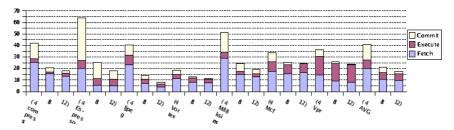

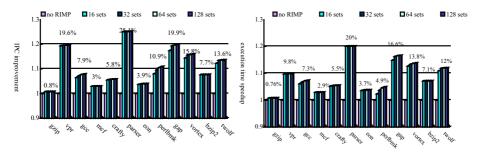

Because we implement two mechanisms to allocate shared resources in our policy, we will first compare RG-FP-S with RG-FP-D. After that, we compare our policy with some fetch policies used widely, including STALL, FLUSH, DG, PDG and DWarn.

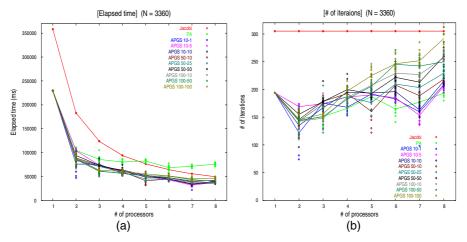

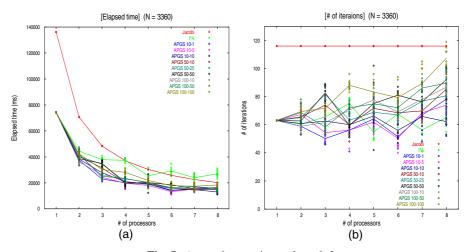

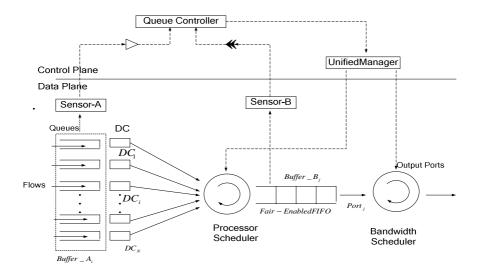

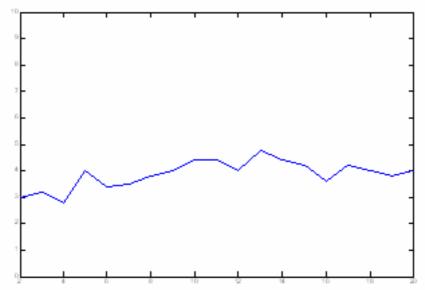

#### 5.1 RG-FP-S vs. RG-FP-D

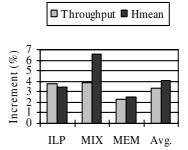

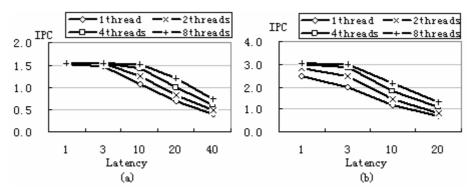

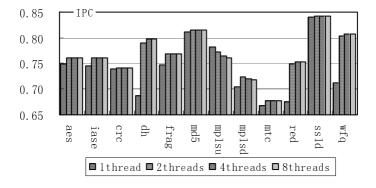

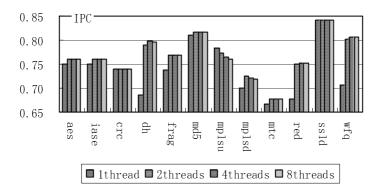

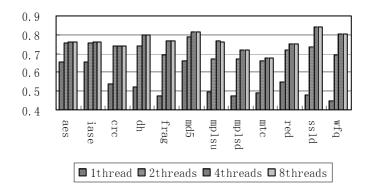

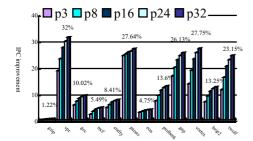

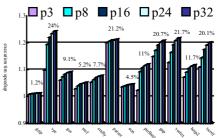

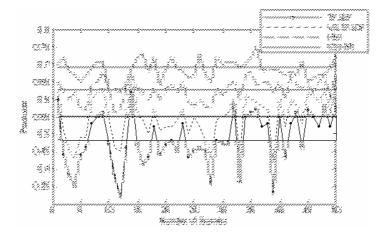

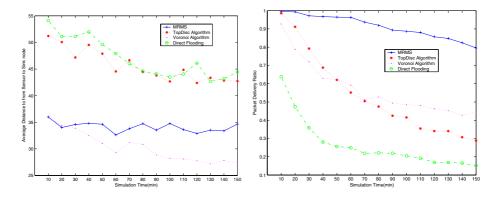

Figure 2 shows the throughput/Hmean results of RG-FP-D compared to RG-FP-S. We can see that RG-FP-D outperforms RG-FP-S in both throughput and fairness, by 3.3% and 4.2% on average, respectively. This is because when deciding the number of resources that a thread can use, static resource allocation only examines the cache behaviors of this thread, and ignores the other one. While dynamic resource allocation examines the two threads simultaneously. Therefore, DRA can make better use of the shared resources.

The results also show that the improvement of RG-FP-D over RG-FP-S is higher for MIX workloads, especially in fairness. The key point is that from Table 1, we can see that only when the fetch priority of two threads is not equal, are there differences between SRA and DRA. Table 5 gives how often threads in two-thread workloads are either at the same fetch priority or at different fetch priority. We can see that for MIX workloads, it is more common that two threads are at different priority levels than ILP and MEM workloads.

**Table 5.** Distribution of threads in fetch priority for two-thread workloads

| Workload | The same | Different |

|----------|----------|-----------|

| Type     | level    | Level     |

| ILP      | 53.8     | 46.2      |

| MIX      | 24.8     | 75.2      |

| MEM      | 64.4     | 35.6      |

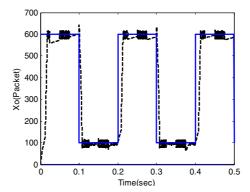

**Fig. 2.** Throughput/Hmean results of RG-FP-D compared to RG-FP-S

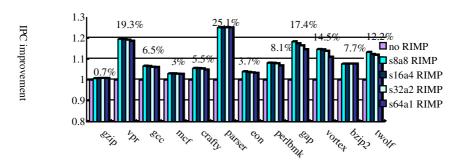

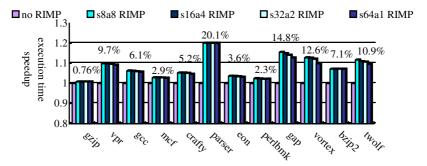

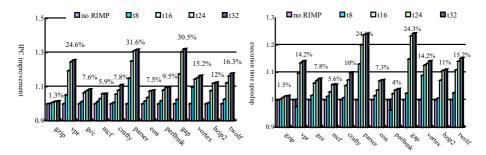

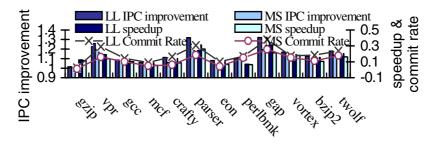

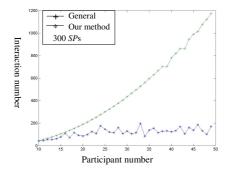

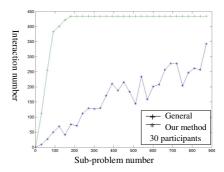

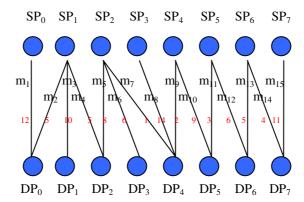

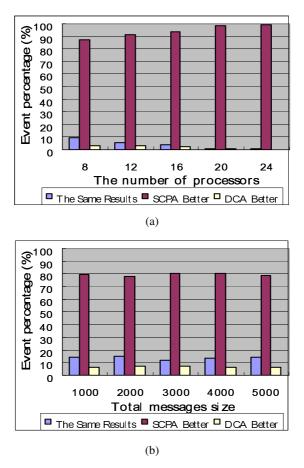

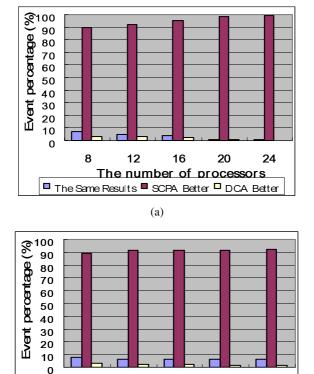

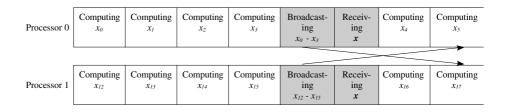

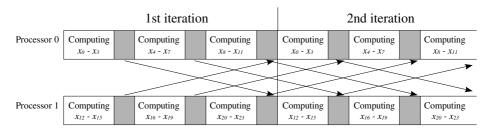

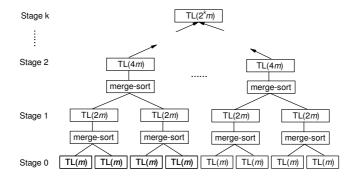

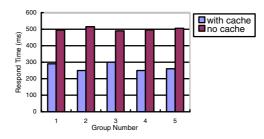

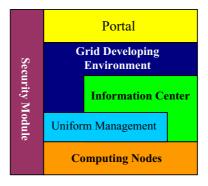

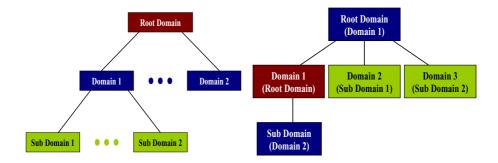

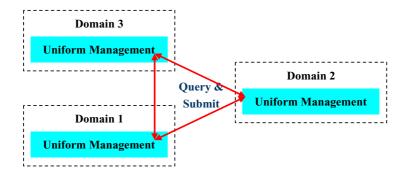

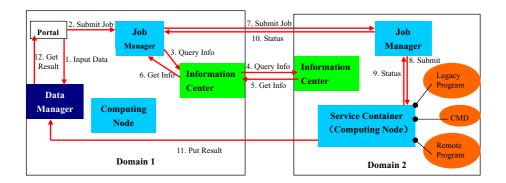

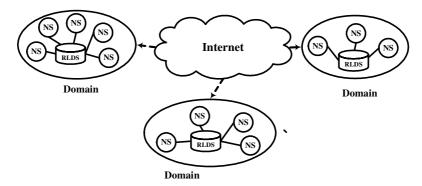

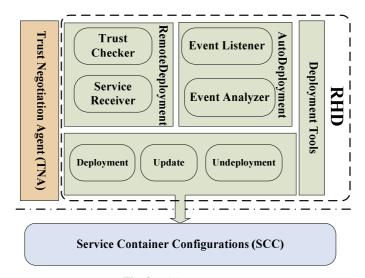

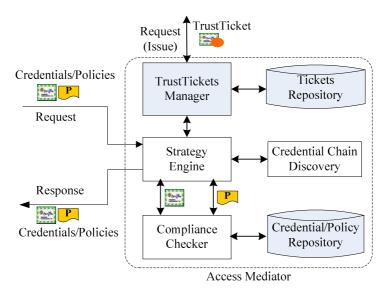

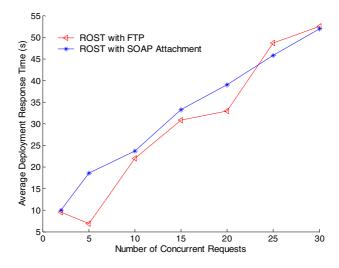

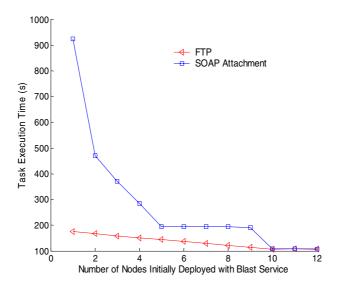

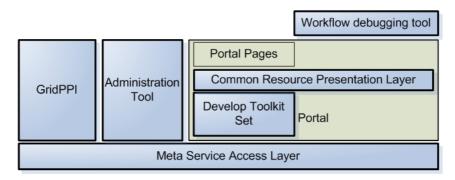

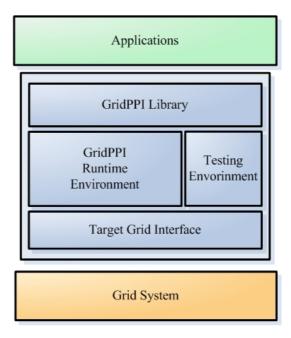

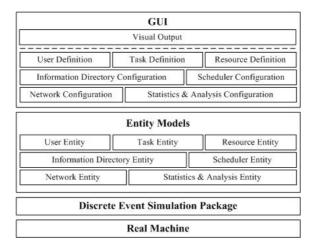

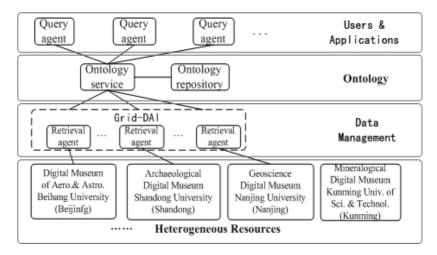

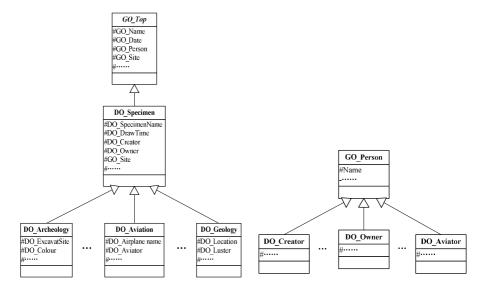

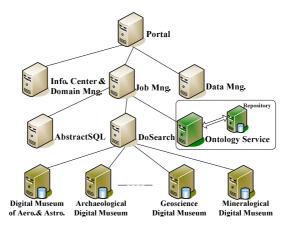

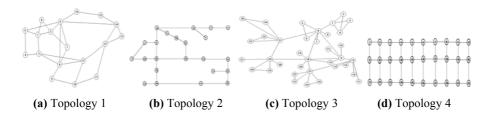

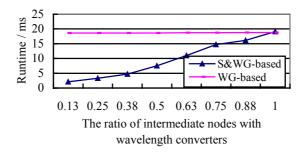

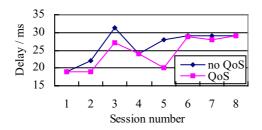

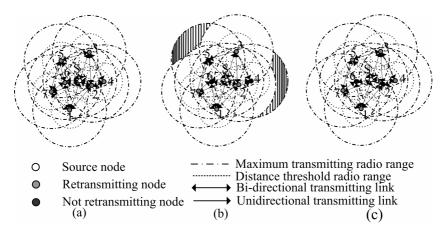

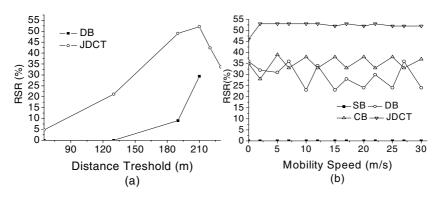

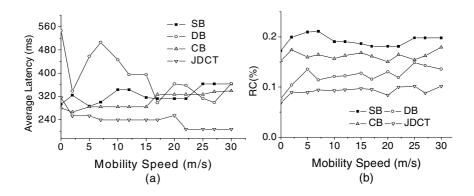

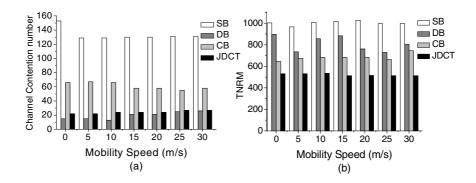

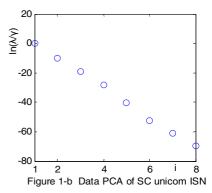

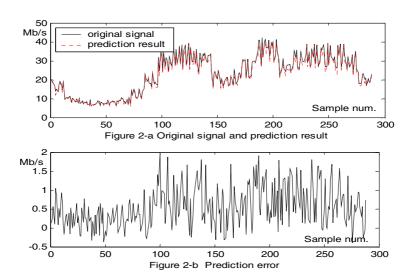

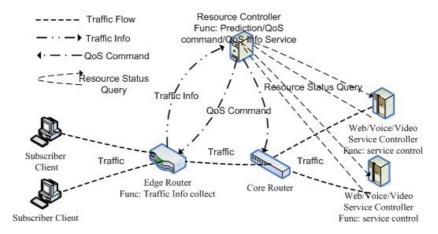

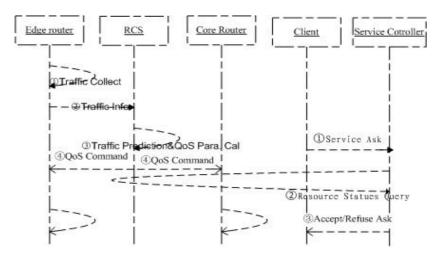

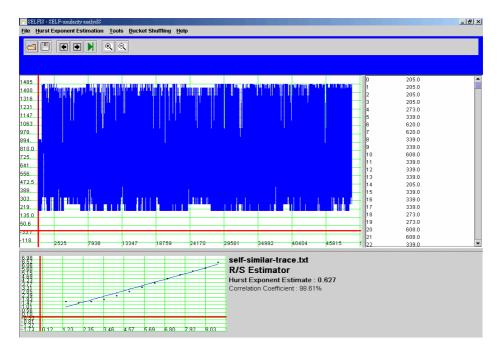

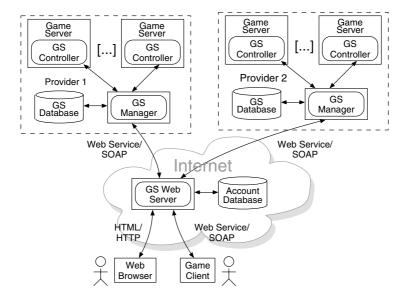

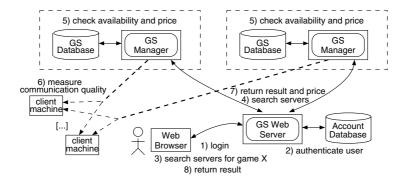

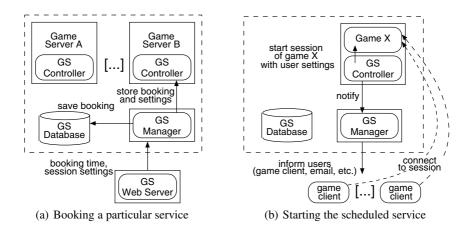

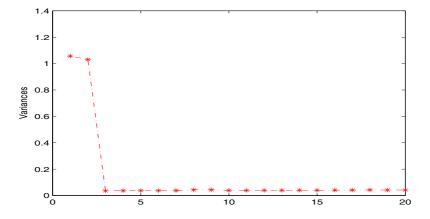

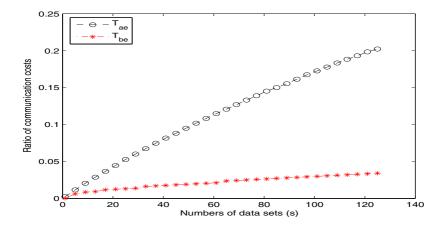

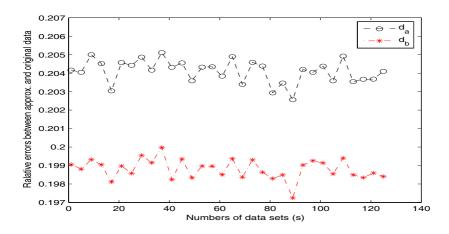

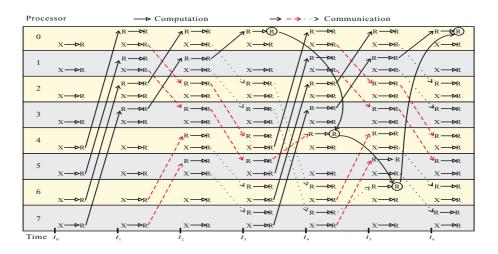

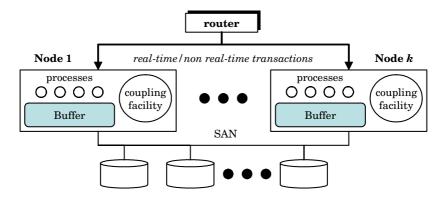

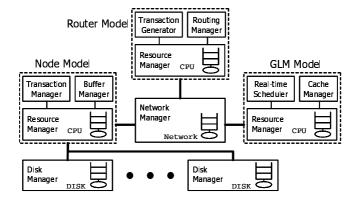

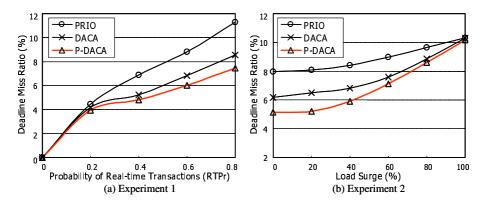

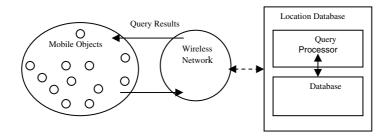

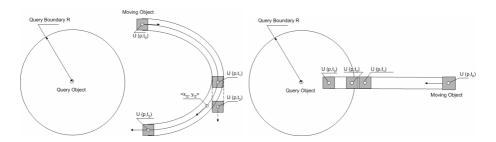

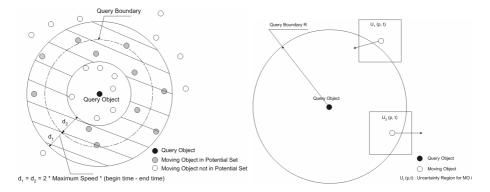

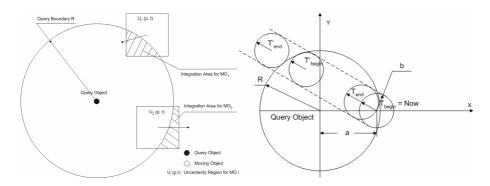

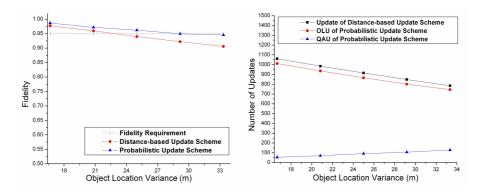

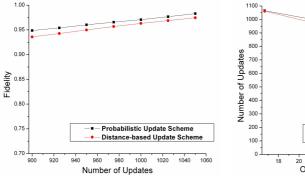

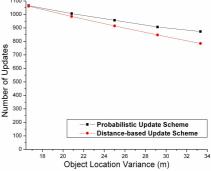

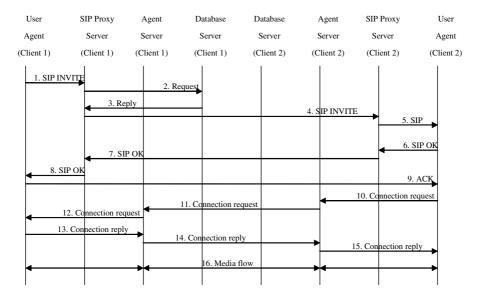

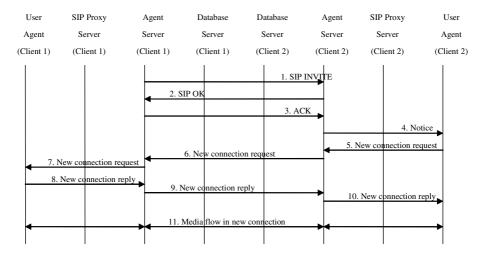

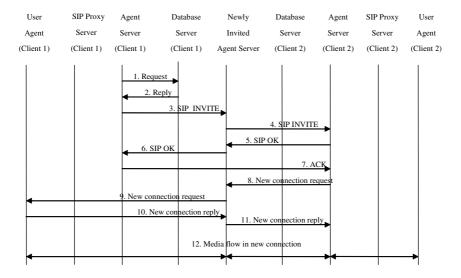

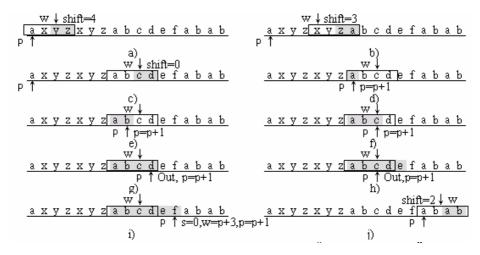

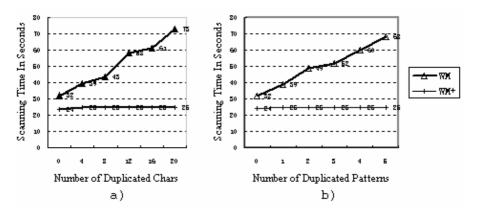

#### 5.2 RG-FP vs. Other Policies